AMD Announces Zen 4 EPYC Embedded 9004 Series: Up to 96 Cores With 1P and 2P Solutions

by Gavin Bonshor on March 14, 2023 4:00 AM EST

While AMD's portfolio of embedded products doesn't receive quite as much attention as it should, it's not a product lineup to be underestimated. AMD's "fourth platform" covers a surprisingly wide range of chips for embedded devices and applications, ranging from miniscule chips for industrial computers and edge devices, all the way up to mighty EPYC processors designed for high throughput workloads. It's the latter that AMD is focusing on today, as Embedded World 2023 kicks off. A key fixture in the global trade show season for highlighting and releasing embedded and IoT solutions, AMD is using the show to unveil its EPYC Embedded 9004 series, its next generation of embedded processors based on its highly efficient Zen 4 microarchitecture.

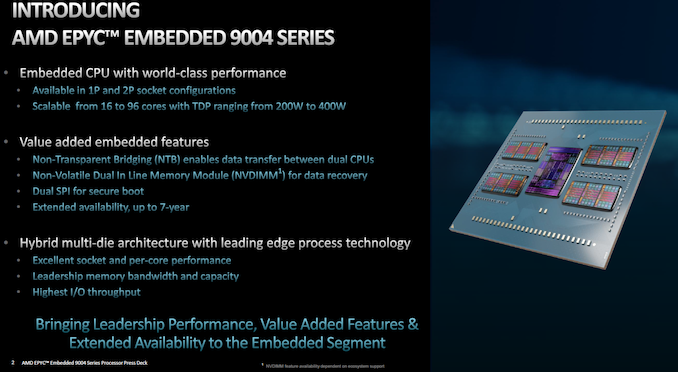

Derived from AMD's standard EPYC 9004 chips for servers, the AMD EPYC Embedded 9004 processors are aimed at embedded applications such as automation, telecommunications, the Internet of Things (IoT), and edge computing; use cases where high power efficiency is a strict technical requirement. Coming with options in both 1P and 2P configurations, AMD's EPYC Embedded 9004 series processors feature up to 96 cores (192 threads) per chip, with up to 384 MB of L3 Cache and duodenary (12) channel memory controllers, which are capable of supporting DDR5-4800 ECC memory in RDIMM, NVDIMM-N, and 3DS RDIMMs flavors.

AMD EPYC Embedded 9004 Series: Up to 96 Cores, up to 400 W cTDP

AMD's EYPC Embedded processors are deployed for various applications and industries. One of the most profound use cases includes the industrial automation industry, where large computing power is required and can subsequently process large amounts of data in real time. Other industries requiring high-powered and highly efficient embedded solutions include the medical imaging industry, edge computing, networking, and telecommunications.

Two critical requirements for embedded solutions are power efficiency and performance per watt, which is why the latest EPYC embedded 9004 chips must be fit for purpose. Built upon AMD's recently released "Genoa" EPYC 9004 server processors, AMD has assembled ten new SKUs for the embedded market, focusing on delivering leading-edge performance while maintaining unparalleled performance to power efficiency. The bulk of these parts should look familiar to regular EPYC users – many of the SKUs are essentially embedded-class versions of existing EPYC 9004 parts, with the additional features and availability guarantees that being an embedded-class product entails.

Overall, the AMD EPYC Embedded 9004 stack consists of six 2P processors with options ranging from 16C/32T to large scaled two socket deployments with up to 96C/192T, meaning that a single system can deploy a solution with up to 192 cores with 384 threads. These 2P systems, which require more PCIe 5.0 lanes, can also be configured with base models of up to 16C/32T (EPYC 9124), 24C/48T (EPYC 9254), as well as 32C/64T (EPYC 9354), 48C/96T (EPUC 9454) and 64C/128T (EPYC 9554) can be deployed in dual socket SP5 solutions.

| AMD EPYC Embedded 9004 (Genoa) Processors | ||||||||||

| AnandTech | Core/ Thread |

Socket Config |

Base Freq |

1T Freq |

L3 Cache |

PCIe 5.0 |

Memory | TDP (W) |

cTDP (W) |

|

| EPYC 9654 | 96 | 192 | 2P | 2.4 GHz | 3.7 GHz | 384 MB | 128/160 | DDR5-4800 | 360 | 320-400 |

| EPYC 9654P | 96 | 192 | 1P | 2.4 GHz | 3.7 GHz | 384 MB | 128 | DDR5-4800 | 360 | 320-400 |

| EPYC 9554 | 64 | 128 | 2P | 3.1 GHz | 3.75 GHz | 256 MB | 128/160 | DDR5-4800 | 360 | 320-400 |

| EPYC 9554P | 64 | 128 | 1P | 3.1 GHz | 3.75 GHz | 256 MB | 128 | DDR5-4800 | 360 | 320-400 |

| EPYC 9454 | 48 | 96 | 2P | 2.75 GHz | 3.8 GHz | 256 MB | 128/160 | DDR5-4800 | 290 | 240-300 |

| EPYC 9454P | 48 | 96 | 1P | 2.75 GHz | 3.8 GHz | 256 MB | 128 | DDR5-4800 | 290 | 240-300 |

| EPYC 9354 | 32 | 64 | 2P | 3.25 GHz | 3.8 GHz | 256 MB | 128/160 | DDR5-4800 | 280 | 240-300 |

| EPYC 9354P | 32 | 64 | 1P | 3.25 GHz | 3.8 GHz | 256 MB | 128 | DDR5-4800 | 280 | 240-300 |

| EPYC 9254 | 24 | 48 | 2P | 2.9 GHz | 4.15 GHz | 128 MB | 128/160 | DDR5-4800 | 200 | 200-240 |

| EPYC 9124 | 16 | 32 | 2P | 3.0 GHz | 3.7 GHz | 64 MB | 128/160 | DDR5-4800 | 200 | 200-240 |

Digesting the AMD EPYC Embedded 9004 series for single socket applications, there are four 1P SKUs available. The entry-level model for single SP5 socket platforms is the EPYC 9354P with 32 x Zen 4 cores with 48 threads, a base frequency of 3.25 GHz, and a 1T turbo of up to 3.8 GHz. The EPYC 9354P has 256 MB of L3 cache, with a base TDP of 280 W and a cTDP between 240 and 300 W. There is also a 48C/96T model (EPYC 9454P) and a 64C/128T model (EPYC 9554P) available, with all 1P SKUs outside of the EPYC 9654P (96C/192T) coming with 256 MB of L3 cache.

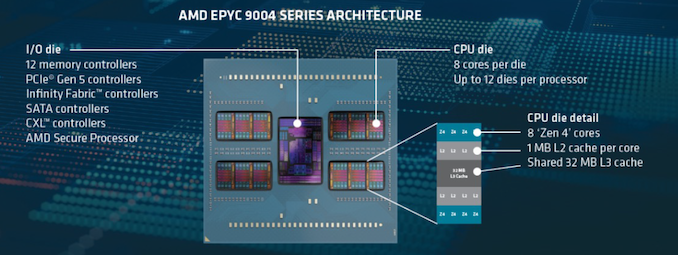

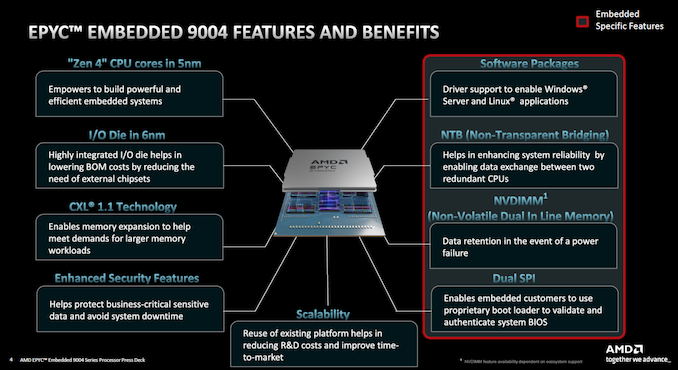

Based on the Zen 4 microarchitecture built on TSMC's 5nm N5 process node, each Core Complex Die (CCD) can accommodate up to eight Zen 4 cores, with 1 MB of L2 cache per core (8 MB per CCD), with up to 32 MB of L3 cache per CCD. The top SKUs in the line-up are the EPYC 9654 and EPYC 9654P, which feature 96 x Zen 4 cores with a total of 384 MB of L3 cache available. Both 96C/192T EPYC Embedded 9654 chips feature a base TDP of 360 W but can be configured for up to 400 W; the lowest is 320 W, where large core clusters are needed but where power restrictions may need to apply.

AMD EPYC Embedded 9004 Series Features: PCIe 5.0, Memory Support, Security, and Software

The single socket (1P) EPYC 9004 embedded SKUs feature 128 x PCIe 5.0 lanes, but dual socket (2P) solutions can be configured to accommodate up to 160 x PCIe 5.0 lanes. This allows systems requiring more storage devices and add-in cards can be deployed, including accelerators, discrete graphics, and networking. AMD is using a TSMC N6 (6 nm) IOD operating as the chips plexus, which reduces the overall cost of deployment because external chipsets aren't a function requirement. According to AMD, the central IOD provides "ample" I/O connectivity, including additional ASICs or controllers to be installed for added flexibility.

Concerning memory compatibility, all EPYC Embedded 9004 SKUs can support up to DDR5-4800 ECC memory, with RDIMMs, 3DS RDIMMs, and unique to embedded lineup, NVDIMMs, all supported. All the chips support twelve-channel memory, although they offer memory interleaving with 2, 4, 6, 8, 10, and 12-channel capabilities depending on the memory density requirements. Each memory channel can support two DIMMs, with a maximum yield of up to 6 TB per socket. AMD states that each socket can support up to 6 TB, so dual-socket SP5 with EPYC Embedded 9004 systems can accommodate 12 TB.

Some specific embedded features include Non-Transparent Bridging (NTB), which connects multiple processors with high bandwidth and high-speed communication via PCIe lanes and devices. Typically used in HPC and other high availability systems, the non-transparent element allows the EPYC Embedded 9004 CPUs to communicate as if they were combined physically and not logically. AMD uses its Scalable Data Fabric (SDF) to interconnect the CCDs with the IOD and memory interfaces. At the same time, the Scalable Control Fabric (SCF) allows a configurable access path to all the blocks on the chip.

AMD's Secure Processor technology, including features like Secure Boot, is built into the die. Secure Boot supports SME-MK (memory) and SEV-MK (virtualization) technologies allowing hardware-level memory and virtualization encryption. The added support of Dual SPI enables customers to use a propriety boot loader to authenticate and validate the system BIOS.

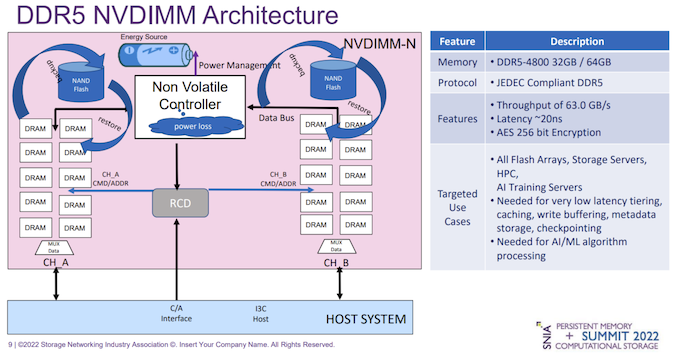

As previously noted, the EPYC Embedded lineup also brings with it official support for NVDIMMs. Specifically AMD EPYC Embedded 9004 supports NVDIMM-N memory (DRAM DIMMs with on-DIMM flash memory backup) to enhance server uptime and state recovery. NVDIMM-N combines the benefits of typical non-volatile memory with NAND flash memory integrated into it as a fail-safe.

DDR5 NVDIMM-N architecture diagram (source SNIA)

One of the main advantages of NVDIMM-N over other types of NVDIMMs is its fast access time. Since DRAM is the primary memory, NVDIMM-N provides high-speed access to data, which is crucial for applications that require fast data access, such as databases and real-time analytics. With the the non-volatile flash storage available as a backup mechanism, NVDIMM-N can ensure that data not lost even during a power failure or system crash. NVDIMM-N also has a lower latency than traditional non-volatile memory, which means that data can be accessed quicker, even at full load, for critical industries such as Cloud storage, Networking, and Telecomms, and even in sectors such as Automotive; all of these are key target segments for the AMD EPYC Embedded 9004 solutions.

And, of course, AMD's first generation of CXL support is available as well. With full CXL 1.1 support, Embedded EPYC processors can access volatile and non-volatile CXL.mem devices, expanding the number and types of memory options available to the platform.

AMD EPYC Embedded 9004 Series Availability and Deployment

Two of AMD's key customers and integrators of its Embedded solutions include Siemens and Advantech, with both companies currently offering solutions to their customers. Siemens's latest SIMATIC IPC RS-828A server is one such deployment that focuses on various workloads, including automotive manufacturing, 5G base stations, and public clouds for IoT solutions.

Advantech also has the latest ASMB-831 server board for the release of the EPYC Embedded 9004 series processors, with an HPC-7485 4U rackmount. The ASMB-831 features five PCIe 5.0 x16 slots and two PCIe 5.0 x8 slots capable of housing four double-decked cards with support for DDR5-4800 ECC RDIMMs, and six slots with a maximum capacity of up to 384 GB.

The AMD EPYC Embedded 9004 Series is available for sampling, while production shipments are expected to begin in April 2023. AMD states that evaluation kits with a reference board, detailed documentation, and tool kits are available now but to qualified customers only. Finally, as these are embedded-class products, AMD is guaranteeing up to 7 years of planned availability for their EPYC Embedded 9004 processors, meaning that replacement chips will be readily available right up to the next decade.

14 Comments

View All Comments

schujj07 - Tuesday, March 14, 2023 - link

Too bad there isn't a 16c/32t single socket version.brucethemoose - Wednesday, March 15, 2023 - link

The desktop Ryzen die makes more sense because its way more power efficient.If you *really* need EPYC's IO in 16C, then shelling out for the 2P chip is probably a drop in the bucket anyway.

schujj07 - Thursday, March 16, 2023 - link

You are paying for support, more validation, ECC, etc... by going with the Epyc. Don't forget that 1st Gen Epyc embedded went from 4c/4t > 16c/32t. There is a market for 8c/16t server class embedded CPUs. These things need the assurance that the CPU is designed to run 24/7 for years on end. A desktop CPU is not designed for that type of usage.brucethemoose - Friday, March 17, 2023 - link

Agreed. To be clear I meant an embedded variant of the desktop silicon, not the actual Ryzen product line.What I am saying is the EPYC IO die is now too big and power hungry for low core count embedded CPUs.

Foeketijn - Tuesday, March 14, 2023 - link

Please AMD, give us cheap and efficient. Like in the Microserver gen10. All the recent embedded parts are so incredibly expensive. 4 cores 15 Watts is enough. But under 150 euro including a dual nic ITX board.Samus - Wednesday, March 15, 2023 - link

Especially with how well Zen4 scales down. It's nearly 80% performance when locked at 40% of its TDP.GreenReaper - Friday, March 24, 2023 - link

Gen8 (Ivy Bridge) was even better in some respects, mine's still going strong with an i5-3470T - only two cores, but four threads at least. Got it for about 160 GBP - someone bought too many.Bruzzone - Tuesday, March 14, 2023 - link

Genoa sample volume available in the channel since 1.7.23 at 6.5% of Milan. On Sapphire Rapids applied computer science project leaving a commercial market volume void, BIG opportunity for AMD to drive 20 M units of Epyc into the enterprise market between Milan and genoa through the end of the year. Mike Bruzzone, Camp Marketingbrucethemoose - Tuesday, March 14, 2023 - link

240W for 32C. 7.5W per core... I know I/O is eating a lot, but that still doesn't seem like a perf/W sweetspot.The 96C part is 3.3W per core at 320W, which is more like it.

trivik12 - Wednesday, March 15, 2023 - link

I saw semiaccurate article about 2 DPC ram issues for Genoa? Is that resolved here. Based on Charile it will take until H2 of this year and that is impacting ramp at CSP. its not just Charlie. Patrick Moorehead also mentioned it and it came up in recent AMD financial conference.