Samsung Foundry Announces 10nm SoC In Mass-Production

by Andrei Frumusanu on October 17, 2016 5:40 AM EST- Posted in

- Semiconductors

- Samsung

- fabrication

- 10LPE

Today Samsung announced mass production of a SoC built on its third-generation 10nm "10LPE" manufacturing node. It was only this January that Samsung announced mass production of its 14LPP process that ended up being used in the Exynos 8890 and the Snapdragon 820 powering up a large amount of flagship devices this year.

This time around the announcement comes quite early compared to the past 2 years and I wasn't expecting any news from the foundry till maybe later in the quarter. This does however bode well for the SoCs built on the process as they seem they'll be able to easily make the spring 2017 device release schedule.

There wasn't any specification as to what kind of SoC the mass production announcement is refering to, but it's very likely we're talking about S.LSI's next generation Exynos - or maybe even Qualcomm's Snapdragon 820 successor, both of which we'll hopefully hear official announcements from in the coming months.

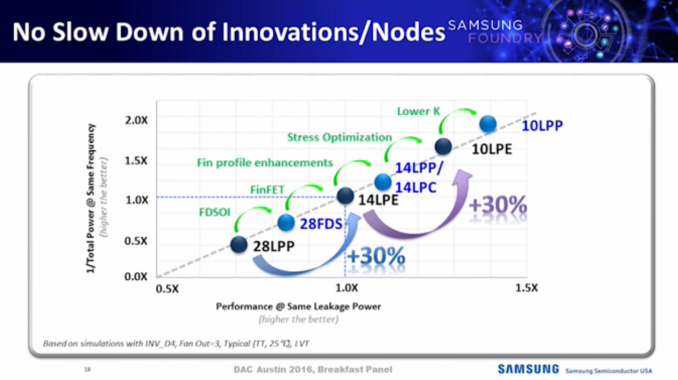

Samsung’s new 10nm FinFET process (10LPE) adopts an advanced 3D transistor structure with additional enhancements in both process technology and design enablement compared to its 14nm predecessor, allowing up to 30-percent increase in area efficiency with 27-percent higher performance or 40-percent lower power consumption. In order to overcome scaling limitations, cutting edge techniques such as triple-patterning to allow bi-directional routing are also used to retain design and routing flexibility from prior nodes.

Credit: DAC 2016 Samsung/Synopsys Breakfast - Ready to Design at 10nm!

The process promises some significant speed and power efficiency advantages over current generation designs so it's likely the next generation of devices will see a large boost, similarly to how the first 14/16 SoCs had large improvements over previous generation 20/28nm designs.

Interestingly the new SoCs will have an edge on recent and upcoming designs still being released on 16nm manufacturing processes, such as Apple's A10 or other TSMC customers who have to wait till next year for 10FF. This presents itself as an opportunity for vendors such as Samsung and Qualcomm to try to close the performance and efficiency gap seen in the current generation through the manufacturing process' good timing.

Source: Press Release

92 Comments

View All Comments

Pork@III - Monday, October 17, 2016 - link

Bravo!azok - Monday, October 17, 2016 - link

Looks like Intel is going to lose the node advantage for mass production.watzupken - Monday, October 17, 2016 - link

What I understood is that the 14nm that Intel is using is different from what the rest of the industry is claiming. Unfortunately, I am not so savvy with the technicalities.azok - Monday, October 17, 2016 - link

I got you, but my suspicion was bolstered after going through this.http://www.fool.com/investing/general/2015/05/18/h...

ddriver - Monday, October 17, 2016 - link

Well, from the looks of it, samsung's fins are as thin as intel's fins, but samsungs transistors apparently require 3 fins, spreading the entire transistor size to about what intel has with two fins at 22 nm. Process is not just a number, it is a "feature size" number, but it is more important how features are put together to form functional components. The more fins you have the more "contact area" and the better the transistor characteristics. Samsung's process might not really be inferior in terms of feature size, but it might be inferior in terms of material properties, thus requiring 50% more fins to achieve satisfactory transistor performance. It also looks like samsung might actually have better topology, that is physically more accurate feature formation.Toss3 - Monday, October 17, 2016 - link

They've also modified it after that article was written, so it could be that it has gotten a lot better: https://news.samsung.com/global/samsung-announces-...Anato - Monday, October 17, 2016 - link

There isn't much point comparing manufacturing feature size as there are tons of other stuff that will affect final product. More important, but harder to compare is the final product and its performance, power consumption and price (PPP). Thats what matters, not the feature size, which is only loosely connected to PPP.azok - Monday, October 17, 2016 - link

Samsung's ability to get the new process ready in relatively less timeframe is worth a pat. Though Intel announced their 10 nm strategy last year, their red-tapism will surely result in delayed implementation. They should try to see what's happening in their rivals' camp. A lot had changed every since rampant Android and parties took over the world.name99 - Monday, October 17, 2016 - link

Just FYI, Samsung's and TSMC's timelines for 10nm are pretty much the same.It seems like the A10X will ship on TSMC 10nm, likely Q1 2017, maybe very beginning of Q2.

TSMC also has very aggressive plans for 7nm; certainly the plan right now is for risk production early next year, and likely the A11X in Q1 2018. Then the plan of record is a breather for a 7nm+ in 2019 and 5nm shipping in 2020.

I haven't seen what Samsung has to say, but I imagine their plans are essentially the same, with maybe 6months or so difference for various milestones.

witeken - Tuesday, October 18, 2016 - link

See EETimes: Samsung seems to plan to skip immersion 7nm and directly use EUV at 7nm. This to me seems quite a dangerous move because Samsung's timing at 7nm is entirely dependent on ASML. Especially because EUV is still nowhere near economic viability. For comparison, Intel plans their 7nm in 2020 and is still developing an immersion alternative for it. Just in case.