Intel’s 11th Gen Core Tiger Lake SoC Detailed: SuperFin, Willow Cove and Xe-LP

by Dr. Ian Cutress on August 13, 2020 9:01 AM EST- Posted in

- CPUs

- Intel

- SoCs

- Tiger Lake

- 10+

- Xe-LP

- Willow Cove

- Intel Arch Day 2020

- SuperFin

- 10SF

Tiger Lake Performance and Products

For Tiger Lake, Intel has made some substantial changes over its previous Ice Lake design. If you’ve skipped to the end of this article without reading the pages in between, then in my opinion you should know that new 10nm SuperFin is what I would consider one of the big talking points.

SuperFin and Willow Cove Frequencies

Intel has done away with the 10+ and 10++ naming, and 10nm SuperFin (10SF) has replaced 10+.

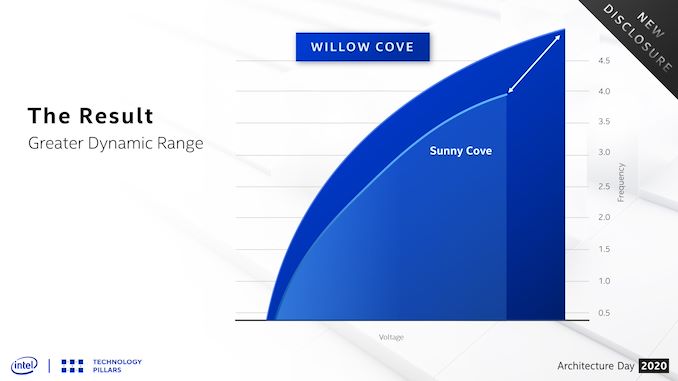

It is called SuperFin because Intel has refined its next generation transistor fins and the metal stack in its manufacturing in order to enable a wider range of performance and efficiency compared to the base 10nm process. What this means is that Intel claims that at the same power as Ice Lake, Intel shows Tiger Lake as having a +10% frequency uplift, going from 4.0 GHz up to 4.5 GHz. Not only this, but because the new 10SF allows a wider range, when the core is pushed, Tiger Lake should move within a hair of 5.0 GHz.

That would be a +20% direct frequency uplift in peak performance, bigger than a traditional intra-node manufacturing update, before we even talk about any microarchitecture improvements.

On the core design front, comparing the new Willow Cove core to the Ice Lake core, we have very few changes. Most of it is identical, except for the L2 cache (+150%, now non-inclusive) and the L3 cache (+50%) getting bigger and new memory security measures being implemented. Intel has quoted that it went after frequency rather than IPC, as +20% frequency is more akin to a node change in performance, whereas chasing IPC in this product would not have produced the same change. As it stands, we predict a small single digit uplift in IPC. We will have to wait until the next generation product to see IPC increase again.

Xe Graphics

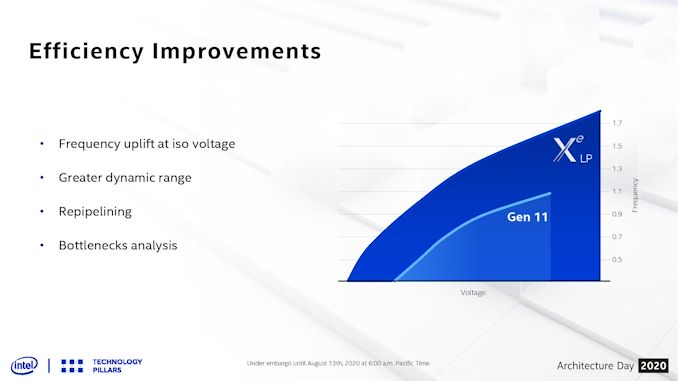

Tiger Lake will also be the launch vehicle for Intel’s Xe Graphics strategy. Onboard we get 96 Xe-LP execution units, up 50% from 64, running at a frequency at least 50% higher, at 1600+ MHz.

Intel is advertising the graphics performance increase over Ice Lake of around 2x all-in. Tiger Lake supports not only DDR4-3200 and LPDDR4X-4267, but LPDDR5-5400 as well, which will be good for 86.4 GB/s of bandwidth that would be great for the integrated graphics. Though it should be noted that laptop vendors aren’t jumping on the LPDDR5 bandwagon immediately, as prices are high and volumes are low / going into smartphones. LPDDR5 is going to be more of a mid-cycle update for Tiger Lake.

The Rest

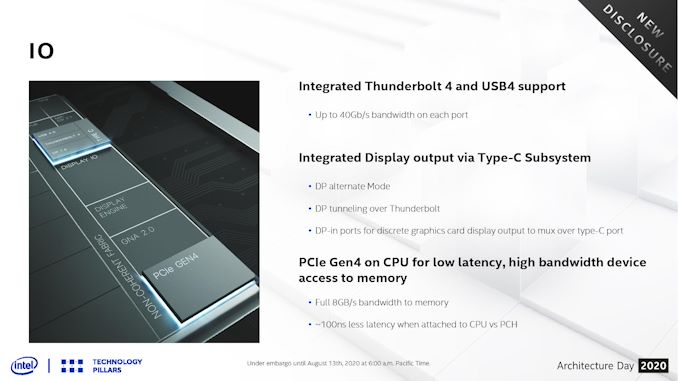

On top of performance, Tiger Lake also expands its IO and Display capabilities, enabling Thunderbolt 4 natively, as well as four 4K displays and support for AV1 decode among other things. Intel states that TGL supports PCIe 4.0, and the amount of lanes will scale with core count (numbers point to an 8-core Tiger Lake in the future). Intel didn’t go into lane counts, but based on a number of pointers on Intel’s slides, we believe the four core version of the chip has a 4.0 x4 link.

The official launch for the Intel’s 11th Gen Core Mobile processors (Tiger Lake) is going to be on September 2nd. At that time we expect to see some of Intel’s OEM partners showcase product designs ahead of Q4 launches in time for the holiday season. There are still a number of questions on the chip, Intel’s ability to manufacture it, how it will compete against AMD, and so forth, which we expect to learn closer to that time.

Tiger Lake on 10 W to 65 W CPUs

As a final thought – one of the first comments made by Intel as part of our briefings was that the Tiger Lake design is going to be scalable, from 10 watts to 65 watts. The current processor we know about today is a four core processor at 15 watts. We’ve already surmised that Intel is preparing an eight core variant, with double the L3 cache, which we suspect to go up to that 65 W mark - however there is a question of where that product would end up. Traditional mobile processors tend to have a ceiling of 45-54 W TDP, and the 65 W space is usually reserved for desktop / socketed processors. Intel previously launched 65 W versions of its Broadwell mobile CPU on the desktop in 2015, and I wonder if we might see something similar here, which would enable Willow Cove, 10SF, and integrated Xe-LP on the desktop.

All of our information today came from Intel’s closed door Architecture Day 2020, held less than 48 hours prior to when this goes public. Aside from my article on Tiger Lake, and Ryan’s article on Intel’s Xe Portfolio, a number of other topics were covered, which we’ll dive into over the next few days.

71 Comments

View All Comments

Quantumz0d - Thursday, August 13, 2020 - link

"The others not mentioned will be split between 7nm and external fabs. More on that info in a separate article"So that means they are going for external fab really. Damn. What a shame. I wonder if that's the CPU or this GPU. Anything is a shame on Intel and that beancounter Bob.

IanCutress - Thursday, August 13, 2020 - link

That's referring to the other tiles of Ponte Vecchio. There are 4. We covered 2.Eliadbu - Thursday, August 13, 2020 - link

Shame is when you don't acknowledge your problems and how they might limit you. Going with external fabs allows the company to be competitive where it needs the most. But they sure need a long term strategy and and make critical decisions like which processes they would utilize earlier.Kangal - Thursday, August 13, 2020 - link

It's only GPU.And it's only the Xe-HP (ergo Discreet GPU) variant.

It seems to imply that is only on the 10SFE "enhanced" variant. Basically using TSMC 7nm process for the higher memory and connector chips, named as "Rambo Cache" and "Xe Link". And that's targeting the server market and high-end desktops (ie think Nvidia Titan).

Seems like Intel realise how embarrassing it is to ask for their competitors wafers for their main product, so instead they're taking a half-measure and using it for the GPU only. That way they get to save face and say "well, AMD and Nvidia do it too". Also it seems they couldn't get any good prices, which is why only some chips are made on the 7nm, and rest are made in-house on 10nm. Overall, this is Intel playing hard to catch up to TSMC's 7nm and AMD's Zen2 and AMD's Vega. That's why the whole thing is difficult to understand, as it is purposely obfuscated. Yet these will only ship in (late) 2021, whereas the competition is posied to actually leap ahead in 2020 to +7nm TSMC, Zen3, RDNA2. And when Intel arrives, they might even be facing off against 5nm and a Zen3+ refresh. Just to put things into perspective.

tipoo - Thursday, August 13, 2020 - link

This reads quite promising. Great writeup."A few angstroms thick" it's hard to even think about the scale of this stuff, that's 0.1 nanometres or 100 picometres. How far from atomic bonding limits?

DrJackMiller - Thursday, August 13, 2020 - link

It's pretty damn close, but that depends on the bond :-). For a perhaps more human comparison, that of O-O in Oxygen is 1.208 Å; and in C=O bonds (e.g. in CO2) it's around 1.16 Å.vortmax2 - Friday, August 14, 2020 - link

Would love to see an article here of the next 10-20 years of processors as we enter deeper into the atomic scale. What the next big breakthrough?jospoortvliet - Saturday, August 15, 2020 - link

Less promising is that they went for a four cores design again. With AMD pushing the desktop to 8 with the first Zen you would think they would realize amd would pull the same when going mobile and prepare for it... so is this arrogance thinking their cores are so much better or they control the market? Lack of strategic insight? Or inability to work out things for the yield and cost math?Spunjji - Monday, August 17, 2020 - link

If these cores are as good as they're claiming they are, there will be a legitimate dilemma choosing between 4 Very Fast cores and 8 Really Quite Fast cores.I'd wager that yields are 80% to blame and power is the rest - they have an 8-core Tiger in the works, but it's a 35/45W part and there's nothing firm about a release date yet.

none12345 - Tuesday, August 18, 2020 - link

Depends on the atoms, but for reference how about silicon."Silicon has the diamond cubic crystal structure with a lattice parameter of 0.543 nm. The nearest neighbor distance is 0.235 nm."

Diatomic hydrogen is the smallest molecule with a bond length of 0.74 angstrom.

Bond length is typically 1-2 angstrom.

"Intel states that this is an industry first/leading design, enabled through careful deposition of new Hi-K materials in thin layers, smaller than 0.1nm, to form a superlattice between two or more material types."

Unless im missing something, the above statement does not make any sense to me. thin layers of atoms less then the average bond length between atoms is nonsensical.