USB 3.2 at 20 Gb/s Coming to High-End Desktops This Year

by Anton Shilov on February 26, 2019 1:00 PM EST- Posted in

- Peripherals

- Trade Shows

- USB-C

- USB

- ASMedia

- USB 3.2

- MWC 2019

- Synopsys

Since mid-2017 we've been talking about the impending arrival of USB 3.2, the next version of the USB Implementers Forum's ubiquitous standard for connecting external devices. With 3.2 serving as both an upgrade to the feature set and a physical layer tweak to provide more bandwidth, according to the USB-IF at MWC 2019, the technology will finally come to fruition this year.

According to the organization that sets the standards for the USB interface, discrete USB 3.2 controllers capable of supporting the standard's new 20 Gb/s Type-C mode will be available this year. Being a specification-setting group, the USB Implementers Forum does not name companies that develop actual chips. But given the limited number of companies that develop standalone USB controllers, the names of the suspects are pretty well known.

Since discrete USB controllers are used mostly by high-performance desktop systems, we're likely to see the first USB 3.2 chips to land on high-end motherboards first. In which case we could see motherboard venders showing off product sometimes this summer, or maybe a bit later. Meanwhile peripherals will likely lag a bit for compatibility testing and the like, in which case we'd start seeing them in 2020.

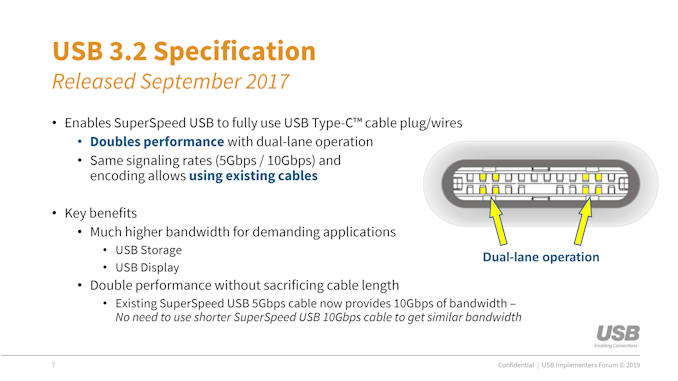

Though technically only a point upgrade for the USB standard, USB 3.2 includes multiple enhancements for the standard in terms of bandwidth, as well as changes to how the standard is branded. In terms of bandwidth, USB 3.2 introduces the ability to use two high-speed USB Type-C Tx/Rx channels – the so-called x2 mode – to get 20 Gbps maximum throughput on a Type-C cable. The technology retains the USB 3.1 physical layer data rates and encoding techniques (SuperSpeed and SuperSpeed+), so while bonding two channels is new, how those individual channels work at a low-level is not.

Meanwhile, USB 3.2 branding will be absorbing the earlier USB 3.0/3.1 branding, as the overriding USB 3.x standard continues to evolve separately of the underlying SuperSpeed encoding technique. As USB 3.2 hosts and devices roll out on the market, we’ll see the branding switch over to USB 3.2 Gen 1 (5Gbps SuperSpeed), USB 3.2 Gen 2 (10Gbps SuperSpeed+), and USB 3.2 Gen2x2 (2x10Gbps SuperSpeed+). So while all future products will be 3.2, they won't necessarily support the higher 10Gbps and 20Gbps data rates. Those decisions are up to the device manufacturer, especially as not all devices need the higher speed modes and the increased build costs that come with them.

Related Reading:

- ASMedia Demos USB 3.2 Gen 2x2 PHY, USB 3.2 Controller Due in 2019

- USB 3.2 Update to Bring 20 Gbps Bandwidth: USB 3.1 Type-C Cables Compulsory

- Cosemi Launches USB 3.1 Gen 2 Hybrid Active Optical Cable: Up to 50 Meters of USB

- Cypress and Zhaoxin Have USB 3.1 Gen 2 USB Controllers

Source: USB Implementers Forum

62 Comments

View All Comments

SaturnusDK - Tuesday, February 26, 2019 - link

Nope. TB3 is not backwards compatible with TB1 and TB1. It's different plugs for one thing, and there are specifically issues when using TB3 to TB1 with a needed converter that some protocols in TB1 are not resolved the same way.And yes, there are huge bandwidth issues on Intel platforms. 40Gbit/s is the full bandwidth of x5 PCIe 3.0 lanes. However, no solutions thus far can even communicate with the CPU with more than the x4 PCIe 3.0 lanes than are the shared connection between the CPU and the PCH on Intel platforms for all PCH to CPU communication. So the theoretical bandwidth can only ever happen between the TB3 controller and another device connected to the PCH with x5 PCIe 3.0 lanes or more.

SaturnusDK - Tuesday, February 26, 2019 - link

Obviously meant TB1 and TB2.TheUnhandledException - Tuesday, February 26, 2019 - link

Um no. TB3 never uses 5 PCIe lanes. It is 4 PCIe lanes. It is 40 Gbps TOTAL (pcie, displayport, usb) muxed together as needed. Not sure where people get this asinine stuff from. Still you are saying 40 Gbps isn't good because 20 Gbps is better. Try using a usb dock vs a TB3 dock and you will suddenly realize you having been talking giberish.SaturnusDK - Tuesday, February 26, 2019 - link

What are you talking about. The total bandwidth equates x5 PCIe 3.0. It doesn't matter how it achieved. A PCIe 3.0 lane has a maximum bandwidth of 1GB/s or 8Gb/s. 40Gbit/s therefore takes the same bandwidth as x5 PCIe 3.0 lanes but there's only x4 PCIe 3.0 lanes between the CPU and PCH in total for all traffic between the CPU and the PCH so it's not really useful for anything other than to other devices connected to the PCH that has more than x5 PCIe lanes available. Are you just trying to be obtuse?voicequal - Tuesday, February 26, 2019 - link

The bottleneck isn't just at the PCH, it's at the Thunderbolt controller itself. Current TB3 controllers only have a x4 PCIe3.0 system interface, so the maximum PCIe bandwidth is limited to ~31.5 Gb/s.But yes, given a different controller implementation, TB3 should theoretically be able to carry 40 Gb/s of PCIe, which would exceed an x4 PCIe3.0 interface.

More info here, but without access to the spec, it still left me with as many questions as answers: thunderbolttechnology.net/sites/default/files/Thunderbolt3_TechBrief_FINAL.pdf

HStewart - Wednesday, February 27, 2019 - link

Backward compatibility with TB1 and TB2 is not that important - it only use in small Apple related systems but important it 100% compatibility with USB3.x on Host but USB 3.x is not compatible with TB3 devices.The big thing about TB3 is mostly in mobile platforms - it seems to be slower on desktops which is honestly more similar to 90's computers than todays

peevee - Tuesday, February 26, 2019 - link

Such controller would require 4x PCIe3 for every port able to operate at full speed in parallel.Which are limited in regular CPUs and chipsets.

Time for PCIe4.

SaturnusDK - Tuesday, February 26, 2019 - link

Well. Fortunately PCIe4.0 is coming to Ryzen 3000 series, sooo...shabby - Tuesday, February 26, 2019 - link

Don't worry, intel is right on it....ikjadoon - Tuesday, February 26, 2019 - link

>So while all future products will be 3.2, they won't necessarily support the higher 10Gbps and 20Gbps data rates.Maybe those ports should still be called USB 3.1, then?

USB-IF should be shown the door for all consumer (aka "marketing") decisions. Only such an incompetent organization could bungle this kind of a once-in-a-generation opportunity.

This is what happens when an organization of engineers and marketers is so disconnected from their consumers.

Why is USB-IF even allowed to pick the marketing name? Most people who can't do a job well....give up.