HiSilicon Announces The Kirin 980: First A76, G76 on 7nm

by Andrei Frumusanu on August 31, 2018 8:30 AM EST- Posted in

- Mobile

- Smartphones

- SoCs

- HiSilicon

- 7nm

- Cortex-A76

- Mali-G76

- Kirin 980

This year at IFA, instead of suddenly finding the new silicon on the show floor, Huawei’s CEO Richard Yu announced this year’s new Kirin 980 during the company’s keynote speech. For readers who’ve been attentively following our articles over the last few months, today’s news should hopefully not come at too big of a surprise, as I’ve been heavily hinting at the timing of the first new 7nm Cortex A76 silicon designs coming later this year in commercial devices, with HiSilicon being the prime candidate for being the first vendor on the market with the their new generation SoC.

Huawei’s silicon design division HiSilicon has been a key strategic component for the company’s products, as it enables it to differentiate itself in a more drastic way than what we usually see from other vendors who simply rely on established open-market SoC vendors such as Qualcomm. This kind of strategy of course is a double-edged sword, as if you’re all-in with your in-house silicon, it also means that these designs must be executed properly, as otherwise you find yourself in an unfavourable competitive position.

The Kirin 950 was an impressive chip as it boasted the first Cortex A72 design on a then new TSMC 16FF manufacturing process – this paid off plenty for Huawei as the combination of new IP as a new manufacturing node resulted in a very competitive silicon which directly translated into favourable characteristics of the handsets in that it was used in.

The Kirin 960 and Kirin 970 on the other hand showcased the risky side of this strategy, and where things can go off-track – the Kirin 960 was a 16nm SoC released in a device generation where 10nm competitors such as the Snapdragon 835 and Exynos 8895 dominated. The Kirin 970 fared better when switching to a 10nm manufacturing node, but this time around HiSilicon wasn’t able to include the newest Arm CPU IP, relying on an A73 CPU while the Snapdragon 845 embraced the new A75. Furthermore the last two Kirin generations had showcased extremely uncompetitive GPU performance and efficiency figures – here HiSilicon is stuck and is at the whim of IP vendors’ ability to produce competitive designs against market leaders such as Qualcomm.

The reason as to why I reiterated what happened to the last few generations, is that this time around HiSilicon finds itself in a very favourable position where IP and manufacturing is aligned into what is essentially a best-case scenario for the new design. Arm’s new Cortex A76 and Mali G76 both promise great leaps in terms of performance and power efficiency, and TSMC is in mass production of its new 7nm manufacturing node.

Today we present the new Kirin 980, the first announced TSMC 7nm SoC as well as the first Cortex A76 and Mali G76 design:

| HiSilicon High-End Kirin SoC Lineup | |||

| SoC | Kirin 980 | Kirin 970 | Kirin 960 |

| CPU | 2x A76 @ 2.60 GHz 2x A76 @ 1.92 GHz @ 512KB L2's 4x A55 @ 1.80 GHz @ 128KB L2's 4MB DSU L3 |

4x A73 @ 2.36 GHz 4x A53 @ 1.84 GHz 2MB L2 |

4x A73 @ 2.36GHz 4x A53 @ 1.84GHz 2MB L2 |

| GPU | ARM Mali-G76MP10 @ 720 MHz |

ARM Mali-G72MP12 @ 746 MHz |

ARM Mali-G71MP8 @ 1037MHz |

| LPDDR4 Memory |

4x 16-bit CH LPDDR4X @ 2133MHz 34.1GB/s |

4x 16-bit CH LPDDR4X @ 1833 MHz 29.9GB/s |

4x 16-bit CH LPDDR4 @ 1866MHz 29.9GB/s |

| Storage I/F | UFS 2.1 | UFS 2.1 | UFS 2.1 |

| ISP/Camera | New Dual ISP +46% speed 10-bit pipeline |

Dual 14-bit ISP | Dual 14-bit ISP (Improved) |

| Encode/Decode | 2160p60 Decode 2160p30 Encode :( |

2160p60 Decode 2160p30 Encode |

1080p H.264 Decode & Encode 2160p30 HEVC Decode |

| Integrated Modem | Kirin 980 Integrated LTE (Category 21/18) DL = 1400 Mbps 4x4 MIMO 3x20MHz CA, 256-QAM (5CA no MIMO) UL = 200 Mbps 2x2 MIMO 1x20MHz CA, 256-QAM |

Kirin 970 Integrated LTE (Category 18/13) DL = 1200 Mbps 5x20MHz CA, 256-QAM UL = 150 Mbps 2x20MHz CA, 64-QAM |

Kirin 960 Integrated LTE (Category 12/13) DL = 600Mbps 4x20MHz CA, 64-QAM UL = 150Mbps 2x20MHz CA, 64-QAM |

| Sensor Hub | i8 | i7 | i6 |

| NPU | Dual @ >2x perf | Yes | No |

| Mfc. Process | TSMC 7nm | TSMC 10nm | TSMC 16nm FFC |

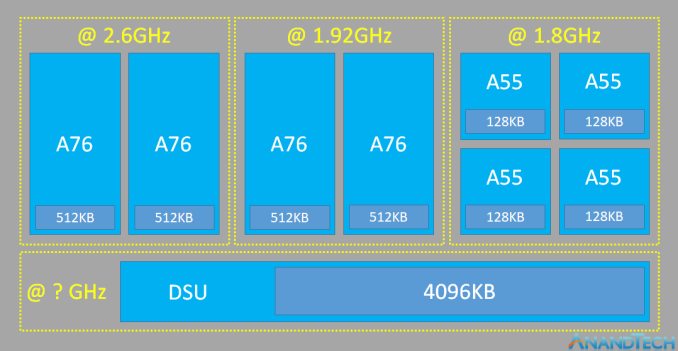

The new Kirin 980 checks off all of the newest available IPs from Arm, finally employing a new DynamIQ CPU cluster configuration comprised of 4 Cortex A76's and 4 Cortex A55s.

The biggest surprise to today’s announcement for me is to see that HiSilicon has made the step forward to fully take advantage of Arm’s new DSU cluster and its asynchronous CPU configuration, and actually implement the brand new Cortex A76 into two groups, each housed in their own clock and voltage plane.

The highest performance Cortex A76 pair runs at up to 2.6GHz. This is less than Arm’s originally announced 3GHz target for the CPU, however I had warned readers to expect more conservative clocks around the 2.5GHz figure, as the higher clock rates seemingly were meant for higher TDP form-factors. Nevertheless, the new CPU microarchitecture still brings with it substantial performance improvements, and thus will still perform very well at 2.6GHz, posting leading performance for this generation.

The surprise of seeing the second pair of Cortex A76 cores running at up to 1.92GHz is actually quite fantastic news for power efficiency. Here we see HiSilicon include what is essentially a “medium” efficiency group of CPUs. Because these two cores are running on a separate clock and voltage plane to the primary performance A76 pair, it means they can operate at different efficiency points, enabling more effective power savings in varied multi-threaded operation.

Previously, quad-core clusters were running on the same clock and voltages, and if there was a single high performance thread requiring a high performance state, it meant that other medium-performance threads were forced to take a power efficiency penalty by needlessly running at this less efficient performance state. By introducing a mid-tier, this effectively eliminates such kind of overhead which is commonly found in real-world applications.

I haven’t been able to confirm this with HiSilicon as of yet, but the reduced clock of this mid pair of A76 would also strongly point out to a possibly different physical implementation with a lower silicon sign-off frequency. This means that even though both pairs of A76’s are the same IP, this mid-pair are very likely to actually be more efficient when running at the same frequency.

Finally, we see four new Cortex A55 cores as the most power-efficient workhorses of the SoC who’ll be able to take the brunt of workloads, running at up to 1.8GHz. Here again, virtue of the mid-performance cluster, HiSilicon is likely able to implement a very power-efficiency focused physical implementation for the A55’s, resulting in clock speeds that in range with current generation A53 and A55 SoCs.

Cache wise, all the Cortex A76’s come with their recommended 512KB L2 cache configurations while the A55’s employ 128KB caches. As a reminder, in the new DynamIQ cluster configuration, the L2 caches for these designs are private to each CPU core. The L3 cache in the DSU has seen a full implementation at 4MB, double that of what we’ve seen in the Snapdragon 845.

I haven’t been able to confirm the frequency of the DSU in the Kirin 980, nor if it actually has a separate clock and voltage plane of its own, here it might be possible that it’s could be on the same plane with the A55’s. Again, that’s just speculation on my part, the other possibility is that we have 4 full clock and voltage planes for the whole CPU complex.

75% higher CPU performance, 58% better efficiency compared to Kirin 970

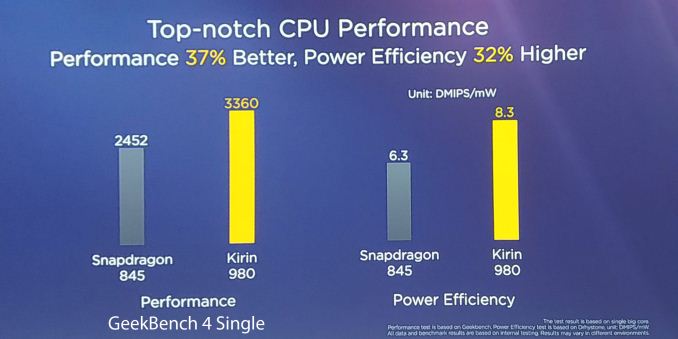

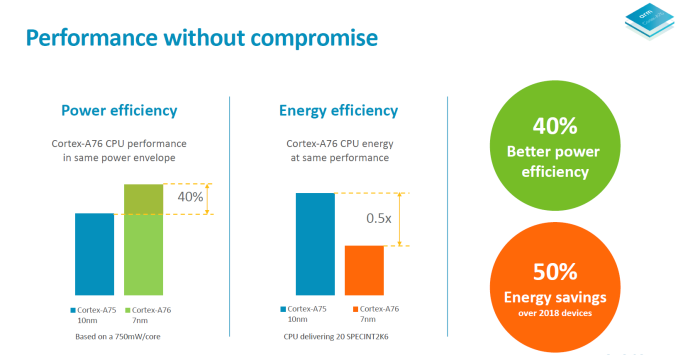

In terms of performance gains, HiSilicon promises 75% gains over the Kirin 970, which after a bit of math actually ends up basically exactly where I had projected the A76 to land, based on Arm’s own performance claims.

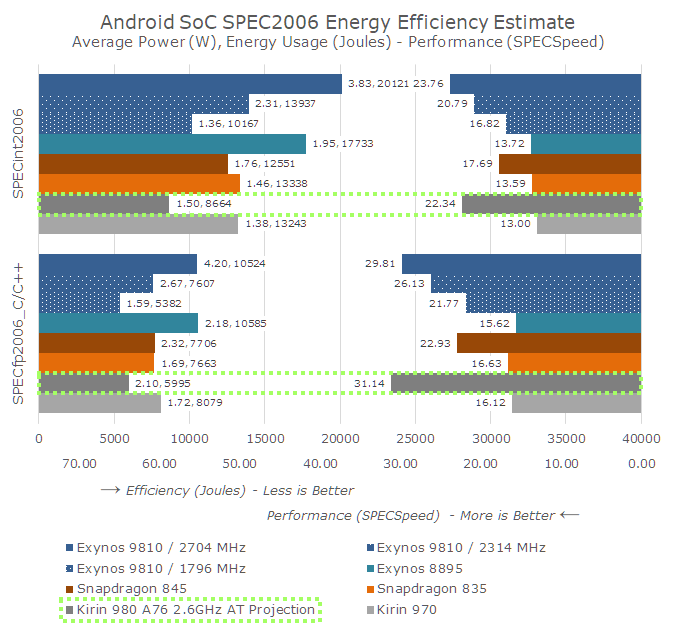

The following projection is of my own, and takes into account both Arm’s and HiSilicon’s matching performance claims:

As you may have noted, the power and efficiency estimates are also included. HiSilicon proclaims that the Kirin 980 is 58% more power efficient than the Kirin 970. We haven’t been able to clarify if this means that the perf/W is 58% better at the same performance of the 970, or if the Kirin 980 has a 58% better perf/W at both SoC’s respective peak performance states. The projection assumes the latter, and it actually again it matches up with Arm’s own claims about the Cortex A76.

I’m still very very sceptical about these numbers as they seem quite fantastic; yet to date I haven’t seen any contradictory information that would actually rebuke these estimates. For the time being, until we actually get our hands on the first Kirin 980 device, take the above power and efficiency estimate with a large grain of salt.

Update Post-Keynote: During the presentation Huawei’s footnotes clarified that the efficiency figures are based on Dhrystone. Dhrystone is very CPU core enclosed and doesn’t stress the rest of the SoC nearly as much in terms of memory traffic, putting some doubts into the above estimates as well as Huawei’s power figures.

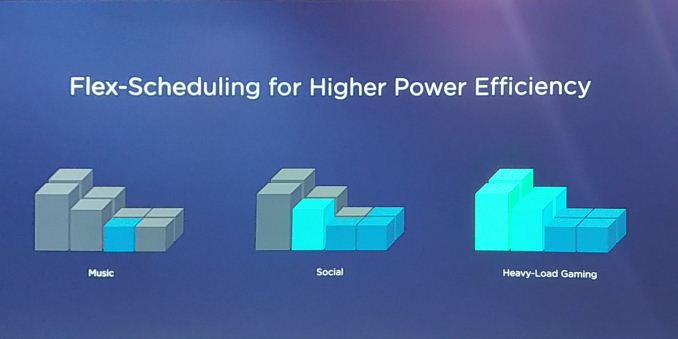

The move to a 3-tier CPU hierarchy also brings with itself complications in terms of scheduling. As we’ve seen this year, scheduling is very much a new critical component of modern SoCs as with the very high dynamic range of performance and power, using the most optimal solution is critical in extracting the best out of the silicon. Here HiSilicon promises a new “Flexible scheduling” mechanism. We unfortunately don’t have any more details on this, but it’s going to be a crucial component of the new Kirin 980.

120 Comments

View All Comments

Wilco1 - Saturday, September 1, 2018 - link

We don't know the die size yet. However don't expect Intel to get anywhere 100mt/mm^2 - the process that will be released will be more like 12nm. And typical densities are significantly lower than claimed, for example Intel's own marketing admits that real TSMC 20nm chips have better density than Intel 14nm.eastcoast_pete - Saturday, September 1, 2018 - link

@Wilco1: Actual vs. theoretical transistor density has been the subject of much discussion for years, if not decades. Your statement about Intel admitting that their 14 nm has lower density than TSMC's 20 nm got me curious. Could you provide a link to a source for that? Would appreciate it - Thanks!Wilco1 - Sunday, September 2, 2018 - link

See https://www.semiwiki.com/forum/files/2015_Investor... page 18.eastcoast_pete - Sunday, September 2, 2018 - link

Thanks for the reference, appreciate it! I looked at the slides, and Intel did say that their 22nm process was defintely below TSMC's 20 nm in transistor density, and their somewhat distorted graph suggests that their 14 nm process (in 2015) was about equal to TSMC's A8-based SoCs in transistor density. They also point out that the ARM SoCs have a large % of elements that are amenable to high density, whereas Intel's CPUs contain a large % of elements that are not (Intel's take on that, not mine). I guess the only true apples-to-apples comparison would be a comparison of either ARM SoCs to ARM SoCs from two different fabs, or x86/x64 CPUs of the same class. Would love to see some slides like this for EPYC vs. Xeon on current nodes.However, the take home message remains: As of 2018, Chipzilla has surrendered the crown of being the most advanced microprocessor manufacturer to TSMC, and Samsung is now 2nd, with Intel dropping to 3rd. I look forward to see how much improvement in power efficiency and speed the move to 7 nm will bring. If the upsides are compelling enough, Intel may regret sitting this one out.

V900 - Monday, September 3, 2018 - link

Nonsense.Intel is still in the lead, though that may change depending on how TSMC delivers on 7nm next year, and whether Intel will sort out their yield issues. (Also next year.)

As of right now; Intels 10nm process has the highest density of any of their competitors, just like Intels 14nm process is well ahead of TSMCs and Samsung’s 14/16nm process.

The chart referred to in the marketing materials is misleading. You can’t compare the density in a power sipping cellphone SOC with the density in a 90W computer CPU (or even 15W laptop CPU.)

(Just one reason why the result you get will be misleading: The density of SRAM cells is 3 times bigger than the density of logic cells. A cellphone SOC contains twice as many SRAM cells than an Intel CPU.)

s.yu - Monday, September 3, 2018 - link

Interesting!Wilco1 - Monday, September 3, 2018 - link

Nonsense. Intel has lost its lead a long time ago. TSMC 10nm beats Intel 14nm by a huge margin (and 14++nm by even more), and 7nm chips will be on the market in a few weeks.That comparison is between actual chips aimed at similar markets, same number of cores, on-chip GPU, similar TDP, similar performance, so it's a much better comparison than theoretical densities.

As of right now there is no Intel 10nm process that is in volume production, we have to wait until next year. But then TSMC will be on their 2nd generation 7nm process.

V900 - Monday, September 3, 2018 - link

LOLOLOL!Look, if you don’t understand why the comparison is meaningless, then I’m not going to waste my time trying to explain a fanboy the difference between a process meant for mobile chips, and one meant for HP desktop CPUs.

The wackiest thing here isn’t just your fanboy hate of Intel (Find a sports team to cheer for, seriously!)

It’s the fact that you’re claiming that TSMCs process is more sense than Intels, when anyone who reads the chart titled “Normalized for composition” can see that it’s clearly not the case, and that Intels 14nm process is significantly more dense than both TSMCs and Samsung’s.

Wilco1 - Monday, September 3, 2018 - link

Congratulations you're the best ever Intel fanboy! If you don't understand why the "normalized decomposition" is pure marketing bullshit hen you're even dumber than it seems.V900 - Monday, September 3, 2018 - link

Of course you have no idea whether Intels 10nm process will be closer to 12nm or not.And your claim that TSMC 20nm chips are more dense than Intels 14nm chips is likewise wrong.

Intels marketing makes no such claim, in fact they make quite the opposite claim: That Intels 14nm handily beats both TSMC and Samsung’s comparable process in density.